HDL을 처음 시작하였을 때 주변에서 알려주는 사람이 없어서 참 많은 삽질을 했었습니다. Modelsim을 이용하여 첫 컴파일 하였던 것이 석사 1학기 여름 방학 때였는데 테스트 벤치 만드는 법도 몰라서 do 화일 안에 force 명령어를 이용하여 시뮬레이션을 하였답니다. ^^;

그래도 MAX Plus 2를 사용하여 시뮬레이션 할 때 일일이 wave를 그려주었던 것에 비하면 얼마나 편하였던지 몇일을 기쁜 마음으로 시뮬레이션 돌려보곤 했었습니다. 지금 생각해보면 크게 어렵지 않은데 당시에는 왜 이리 힘들었는지 모르겠네요 ㅎㅎ

Modelsim은 저에게 로직 설계의 즐거움을 알려준 시뮬레이션 툴입니다. 이 글을 읽는 분들에게는 Modelsim이 어떤 툴인가요?? 이미 능숙하게 사용하시는 분들도 계시겠지만 그렇지 않은 분들을 위하여 간단하게 Modelsim에서 Verilog-HDL을 컴파일 하고 시뮬레이션 하는 방법을 소개 합니다.

첨부 화일을 확인해 보시면 두개의 폴더가 있는데, rtl 폴더에서는 Verilog-HDL 코드를 확인 할 수 있고 fsim 폴더에는 Modelsim으로 function-sim을 하도록 구성해 놓았습니다. 본 글에서는 시뮬레이션 하는 방법을 설명할 것이 때문에 로직 설계와 테스트벤치 및 테스트 벡터 입력 방법은코드를 보시고 직접 이해하시기 바랍니다.

본 예제를 가지고 Modelsim에서 function 시뮬레이션하는 방법은 간단합니다. Modelsim을 실행시켜 change directorty로 fsim 폴더로 이동하신 후에 커멘드 창에 do sim.do 를 입력하시면 컴파일과 시뮬레이션이 자동으로 진행되는 것을 확인 하실 수 있기 때문입니다.

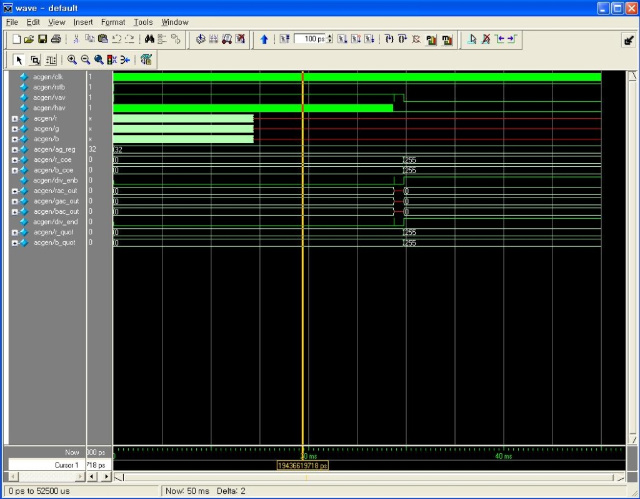

결과는 다음과 같이 wave 창으로 나타날 것입니다.

Modelsim에서 시뮬레이션 하는 과정을 간단하게 설명을 하면

1. library 생성

2. HDL 컴파일

3. 시뮬레이션

4. wave 창에 signal 추가

5. 수행하기

다섯 단계로 나누어 집니다. 그리고 시뮬레이션을 종료하는 방법은 커멘드 창에 quit -sim 을 입렵하면 됩니다. 그럼 sim.do 화일을 열어서 간단하게 시뮬레이션 과정을 알아 보겠습니다. ^^

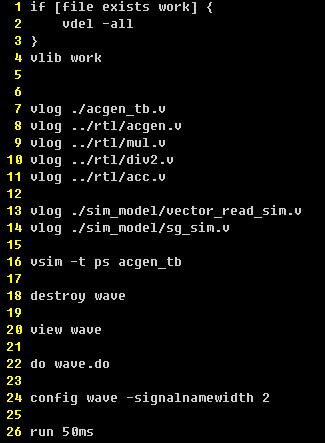

라인 1~4는 컴파일 할 정보를 저장하는 work library를 생성하는 것입니다.

라인 7~14는 시뮬레이션을 할 Verilog-HDL을 Modelsim에서 컴파일 하는 과정입니다. Modelsim에서 Verilog-HDL 코드는 vlog 명령어를 VHDL코드는 vcom 명령어를 사용하여컴파일을 합니다.

라인 16은 시뮬레이션하기 위하여 vsim 명령어를 이용하여 최상위 모듈을 불러 오는 과정입니다.

라인 18~20은 기존에 실행중인 wave 창을 지우고 새로운 wave 창을 불러 오는 것입니다.

라인 22번은 확인 하고 싶은 signal을 wave 창에 띄우는 과정으로 wave.do 화일을 살펴 보시기 바랍니다.

라인 24는 wave 창의 속성을 설정하는 것으로 생략하여도 무관합니다.

라인 26은 50ms 동안 시뮬레이션을 진행하는 것입니다.

이상으로 Modelsim에서 Verilog-HDL의 function 시뮬레이션 하는 방법을 많은 분들에게 도움이 되기를 바라면서 마치겠습니다.

'SoC' 카테고리의 다른 글

| 첫 상용화 칩 - CANTUS (0) | 2009.06.27 |

|---|---|

| IDEC EISC Platform Ver1.0 (0) | 2009.01.04 |

| 새로 개발된 EISC 프로세서 - AE32000C-Empress (1) | 2008.12.10 |

| 좀 더 세밀해져야 할 필요가 있다. (0) | 2008.08.18 |

| 검증의 중요성을 느끼다. (0) | 2008.08.17 |

awb.zip

awb.zip